ADC FLASH (o parallelo)

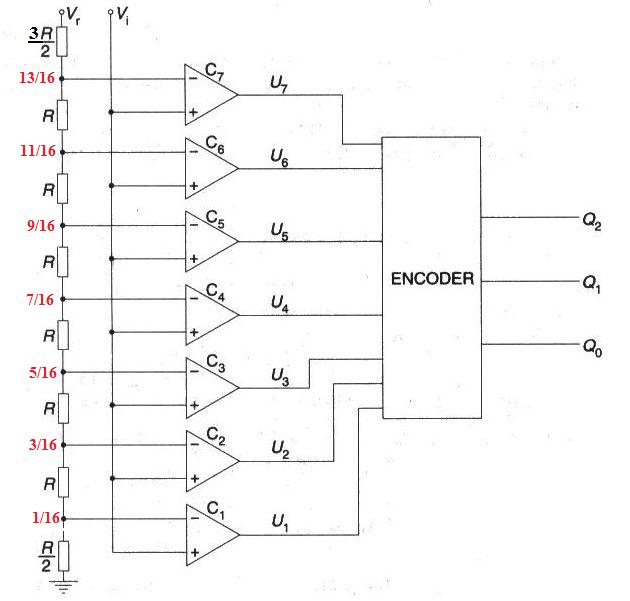

L'ADC flash è il convertitore analogico-digitale più veloce in assoluto, capace di tempi di conversione dell'ordine del nanosecondo. La figura seguente mostra la struttura circuitale di un ADC flash a 3 bit.

Il circuito è composto da 9 resistenze, 7 comparatori e un encoder con 7 ingressi e 3 uscite.

Vr è la tensione di riferimento e Vi è la tensione analogica da convertire. La tensione Vi è collegata sull'ingresso non invertente di tutti i comparatori. L'ingresso invertente di ogni comparatore è collegato invece a un diverso nodo della rete resistiva.

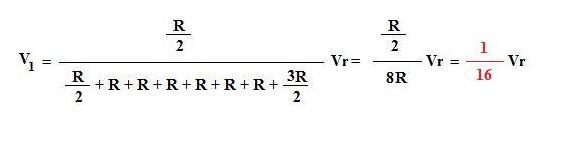

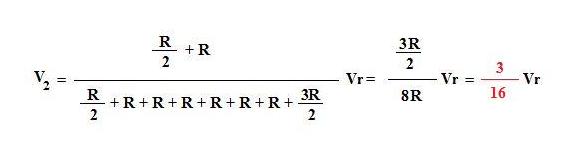

La rete resistiva realizza un partitore di tensione che suddivide la tensione di riferimento Vr nel modo indicato in figura. I numeri scritti in rosso si riferiscono alla frazione di Vr presente su ogni nodo. Per esempio sull'ultimo nodo in basso la tensione vale:

In modo analogo la tensione V2 sul secondo nodo è data da

e così via per i nodi successivi.

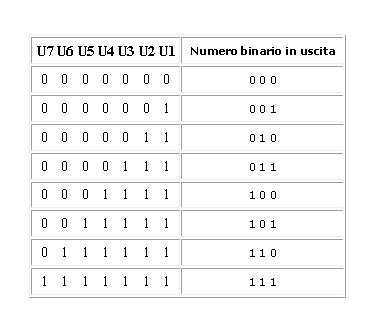

L'uscita di ogni comparatore commuta a livello alto se la tensione analogica Vi supera la tensione di soglia presente sull'ingresso invertente. Per esempio U1 va a livello alto se Vi > 1/16 Vr. Analogamente U2 va a livello alto se Vi > 3/16 Vr e così via. Ma questi valori di tensione rappresentano i confini superiori di ciascun intervallo di quantizzazione (usando una quantizzazione silenziata). Infatti il primo intervallo si estende da 0 fino a Q/2, cioè, usando 3 bit, da 0 fino a Vr/23+1 (da 0 a Vr/16). Analogamente il secondo intervallo di quantizzazione inizia da Vr/16 e arriva fino a Vr/16 + Q = Vr/16 + Vr/8 = 3/16 Vr e così via per gli intervalli successivi.

In sostanza:

- se Vi < 1/16 Vr (tensione che cade nel primo intervallo di quantizzazione), tutte le uscite dei comparatori (U1, U2, ..., U7) sono a livello basso.

- se 1/16 Vr < Vi < 3/16 Vr, solo U1 va a livello alto, mentre U2...U7 rimangono a livello basso.

- se 1/16 Vr < Vi < 5/16 Vr, commutano a livelo alto U1 e U2 (tutti gli altri comparatori rimangono a livello basso).

- così via per tensioni Vi crescenti, finché, con Vi > 13/16 Vr, le uscite di tutti i comparatori sono a livello alto.

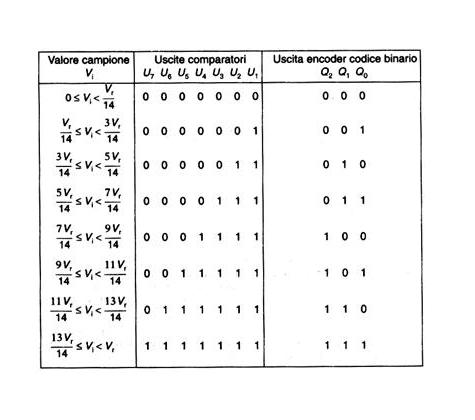

Le uscita dei comparatori sono collegate a un encoder a priorità (priority encoder), il cui scopo è quello di trasformare la sequenza di bit prodotta dai comparatori in un numero binario vero a 3 bit. La codifica prodotta dall'encoder è mostrata nella tabella seguente:

Nonostante l'apparente semplicità circuitale e la grande velocità di conversione (limitata praticamente solo dalla velocità dei comparatori e dell'encoder), la realizzazione di un ADC flash diviene estremamente complessa all'aumentare della risoluzione (numero di bit) del convertitore. Basti pensare che con 8 bit di risoluzione, occorrerebbero 28 - 1 = 155 comparatori diversi e 256 resistenze. Per questa ragione gli ADC flash sono piuttosto costosi e il loro utilizzo è limitato a risoluzioni non troppo elevate (max 10-12 bit).

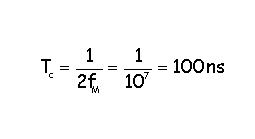

Gli ADC flash sono i convertitori più veloci infatti presentano tempi di conversione dell’ordine delle decine di nanosecondi. Questi convertitori sono necessari quando i segnali hanno frequenza elevata. Sappiamo infatti che Ts deve essere minore del periodo di campionamento. Ora, per un segnale video con fM = 5 MHz, si ha che:

Pertanto il Ts deve essere inferiore. Non si può quindi fare a meno di usare gli ADC flash, gli unici che consentono simili velocità.

Il circuito dell'ADC FLASH è composto da 9 resistenze, 7 comparatori e un encoder con 7 ingressi e 3 uscite.

Nel caso generale di ADC a n bit la struttura fonda-mentale è composta da 2n – 1 comparatori, 2n – 2 resistenze uguali di valo-re R, 2 resistenze di valore R/2 e 1 encoder.

Questi convertitori presentano notevoli problemi costruttivi, essendo difficile ottenerli proprio con 2n – 2 resistenze uguali con stessa tolleranza; ne consegue che il dispositivo ha scarsa precisione oltre a risultare costoso.

Per fare in modo che tutti i dati arrivino contemporaneamente all’encoder ed evitare disturbi (glitch) si possono inserire dopo i comparatori dei latches. Questi mantengono l’informazione e la presentano simultaneamente all’encoder.

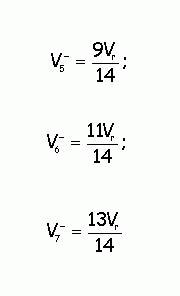

Analizziamo l’esempio di figura 14. I potenziali presenti sui morsetti non invertenti dei comparatori C1, C2, C3, C4, C5, C6, C7 sono rispettivamente:

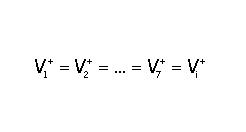

mentre

Ad esempio se:

Vi= 6 Vr / 14

i comparatori C1, C2, C3 hanno l’uscita alta, tutti gli altri bassa. Le uscite U1, U2, U3, U4, U5, U6, U7 valgono 1110000.

L’encoder fornisce il seguente codice binario 011 (equivalente a 3 in decimale, pari al numero di compara-tori con uscita alta).

Spesso è presente un ulteriore comparatore che dà l’indicazione di overflow se Vi > Vr .

Due comparatori flash che si trovano in commercio sono: AD5010KD a 6 bit con Ts = 20 ns e AD6020KD a 6 bit con Ts = 10 ns.