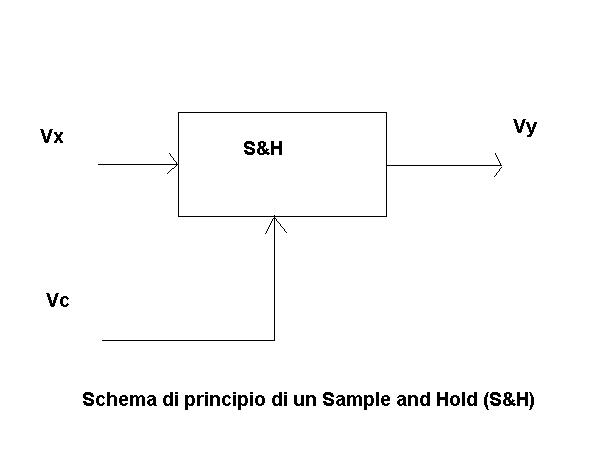

Sample-Hold

Per eseguire correttamente una conversione analogica/numerica (A/D) la tensione all’ingresso (Vx) del convertitore analogico/numerico (ADC) deve rimanere costante per tutta la durata T(ADC) della conversione stessa. Affinché si verifichi ciò è necessario :

f max << 1/ T(ADC) (1.1)

con f max corrispondente alla massima frequenza presente nel segnale analogico da acquisire. In tal caso il segnale può essere ritenuto con buona approssimazione costante durante l’intera durata della conversione.

Se la (1.1) non è soddisfatta si deve impiegare un circuito che campioni la Vx in istanti di tempo prefissati e mantenga il valore campionato per tutto il tempo necessario affinché l’ADC posto a valle di esso esegua la conversione. Tale circuito prende il nome di amplificatore Sample and Hold (SHA), letteralmente “campionatore a tratti”.

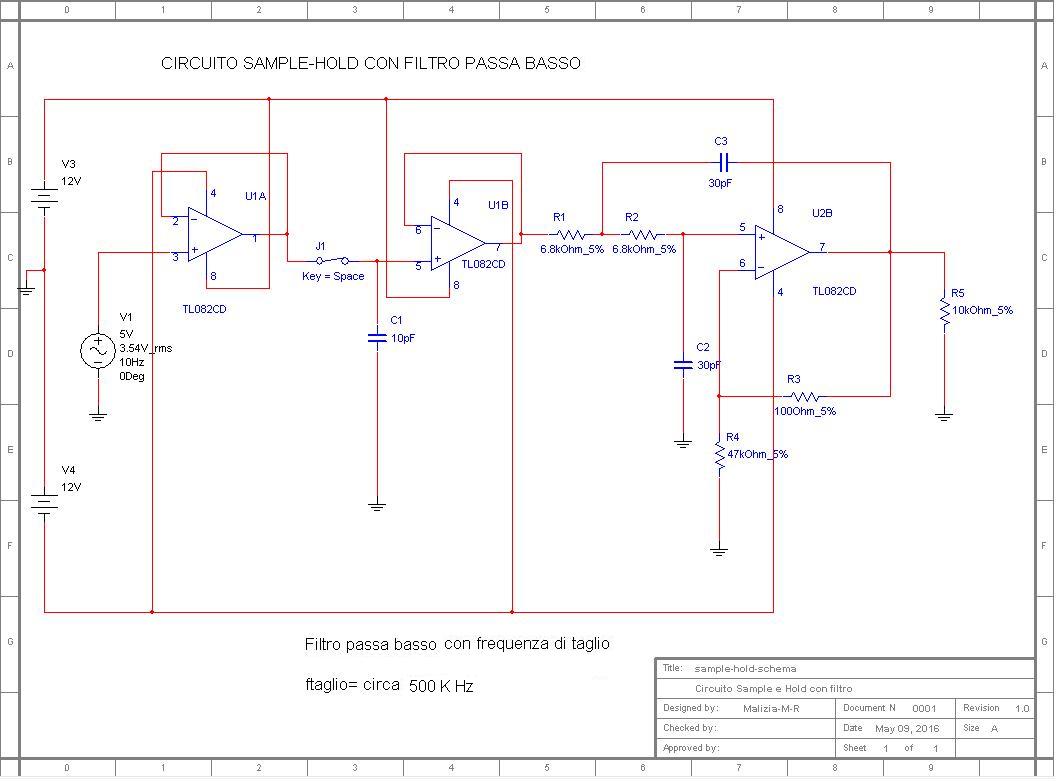

Vediamo adesso come realizzare un circuito Sample &Hold in laboratorio. Prendiamo due amplificatori operazionali TL082, al cui interno ci sono due A.O. integrati). Colleghiamo il primo A.O. in configurazione buffer non invertente in modo da avere alla sua uscita il segnale identico a quello di ingresso.

Vu1= Vi

Colleghiamo l'uscita del primo A.O con un tasto;

Tasto chiuso:

se esso è chiuso il condensatore comincerà a caricarsi fino alla tensione Vu=Vi. L'uscita del secondo amplificatore operazionale, essendo anch'esso in configurazione buffer,quando il condensatore sarà carico,(quasi all'istante), riporterà il segnale di ingresso, cioè Vu2=Vu1=Vi

Vu2=Vu1=V1

Tasto aperto:

Se il tasto è aperto il secondo A.O. riporterà alla sua uscita il segnale Vi2; In questo caso se il condensatore è già scarico l'uscita sarà nulla, altrimenti sarà uguale al valore Vc del condensatore C1.

Schema elettrico del circuito Sample & Hold

Lo schema proposto è quello precedente.

In uscita al secondo A.O abbiamo inserito un A.O. in configurazione filtro del secondo ordine per eliminare eventuali disturbi.

Facendo tutti i conti del filtro si otterrà con i valori proposti una frequenza di taglio di circa 500 KHz .

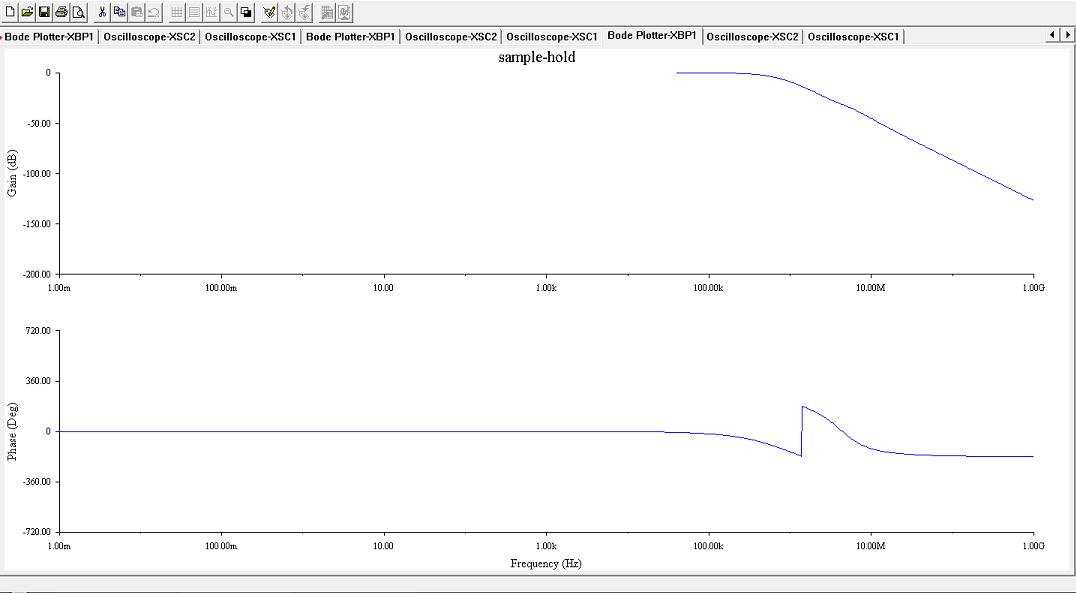

La simulazione con il Multisim dà il seguente grafico del diagramma di Bode del Modulo e della Fase del filtro in uscita dal Sample&Hold.

Diagramma di Bode del modulo e della fase del filtro del Sample&Hold

Per vedere il funzionamento del filtro utilizzato nel circuito Sample & Hold segui il seguente link (pag 23 e pagina 24).